What is CPLD?

CPLDs, which stands for complex programmable logic devices, live up to their promises completely. Essentially, they are designed to emulate multiple PALs (programmable array logic) combined into a single chip and interconnected through a crosspoint switch. Being built on the same technology, utilizing the same programming methods, and using familiar development tools, they can effectively handle more extensive and complex logic operations.

While FPGAs and SPLDs (simple programmable logic devices) are more advanced compared to CPLDs, they operate in a similar manner to CPLDs. CPLDs are more intricate than SPLDs but less complex than FPGAs. The commonly used SPLDs, such as PAL (programmable array logic), PLA (programmable logic array), and GAL (generic array logic), share some similarities with CPLDs.

What is FPGA?

Field programmable gate arrays (FPGAs) are semiconductor devices featuring a customizable logic block (CLB) matrix interconnected by programmable interconnects. What makes FPGAs distinctive is their ability to be reprogrammed after manufacturing, allowing them to adapt to specific application or feature requirements.

FPGA chips have a key distinction from Application-Specific Integrated Circuits (ASICs), which are custom-designed for specific design requirements. This distinguishing feature is the reprogrammability of FPGAs. Unlike ASICs, which have a fixed design, FPGAs can be reconfigured or updated as needed, making them more flexible for adapting to changing design requirements.

Among FPGAs, SRAM-based FPGAs are more popular than one-time programmable (OTP) FPGA development boards due to their ability to be updated multiple times.

FPGAs are structured similarly to gate array ASICs, not like PALs or other traditional programmable devices. They are often used in situations where an ASIC will eventually be deployed, serving as a way to prototype and test the functionality of the ASIC before final production. This allows for design validation and iteration before committing to the higher costs associated with ASIC fabrication.

CPLD Architecture

A CPLD (Complex Programmable Logic Device) is constructed using multiple PAL (Programmable Array Logic) structures referred to as macrocells. It is an evolution of the PAL technology. In a CPLD, each input pin within the package is accessible to every macrocell, but each macrocell has only one output pin. The block diagram of a CPLD illustrates its internal structure.

The block diagram emphasizes that a CPLD consists of numerous macrocells or function blocks. These macrocells are interconnected through a global interconnection matrix (GIM) that is programmable. The rearrangement of the GIM allows for the creation of various logic circuits. CPLDs use digital input and output pins to interface with external hardware. This architecture provides flexibility and reconfigurability for implementing different logic functions based on the specific design requirements.

CPLD Structure

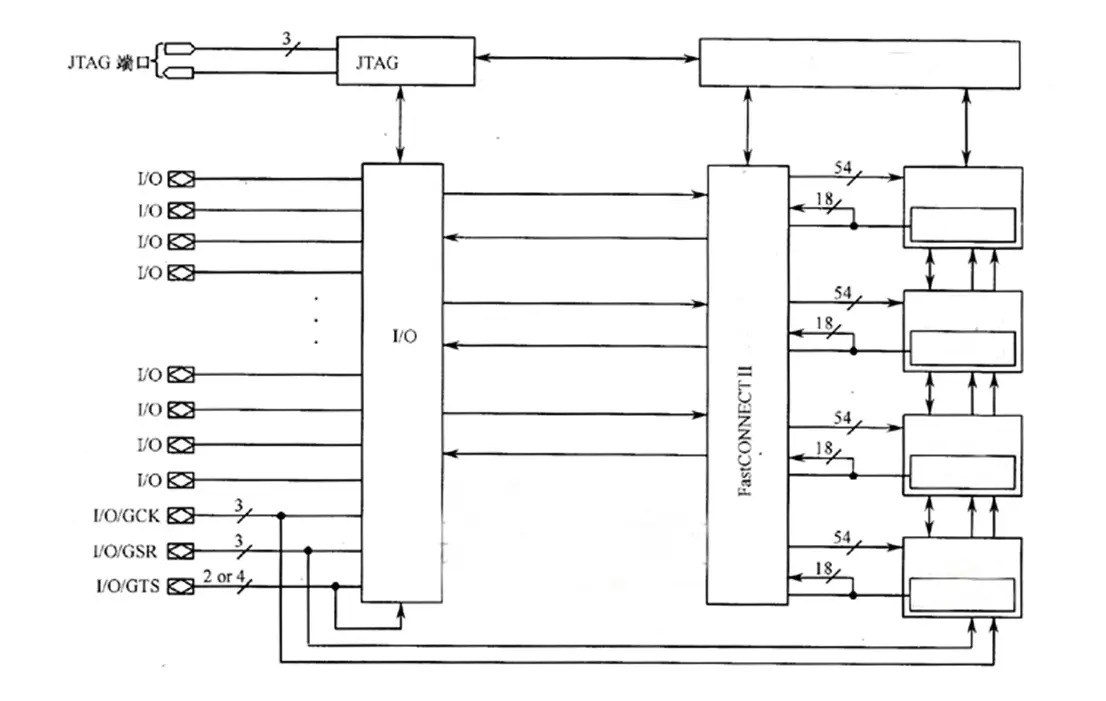

The basic structure of a CPLD, using the Xilinx XC9500XL series chip as an example, is introduced. The CPLD’s architecture is based on the concept of product terms (Product-Term). It comprises three key components: the Function Block, FastCONNECT II SwitchMatrix, and I/O Control Module.

The graphic illustrates the composition of each function block, which includes a programmable array, a product term allocator, and 18 macrocells. These macrocells are fundamental units for executing basic logic operations.

The I/O Control Module is responsible for configuring various electrical properties of the input and output pins, such as open collector outputs and tri-state outputs. Additionally, it manages functions related to input and output.

Furthermore, there are global signals for clock (I/O/GCK), reset (I/O/GSR), and output enable (I/O/GTS), which are connected to each function module within the CPLD via dedicated lines. These global signals provide coordination and synchronization for the CPLD’s operation.

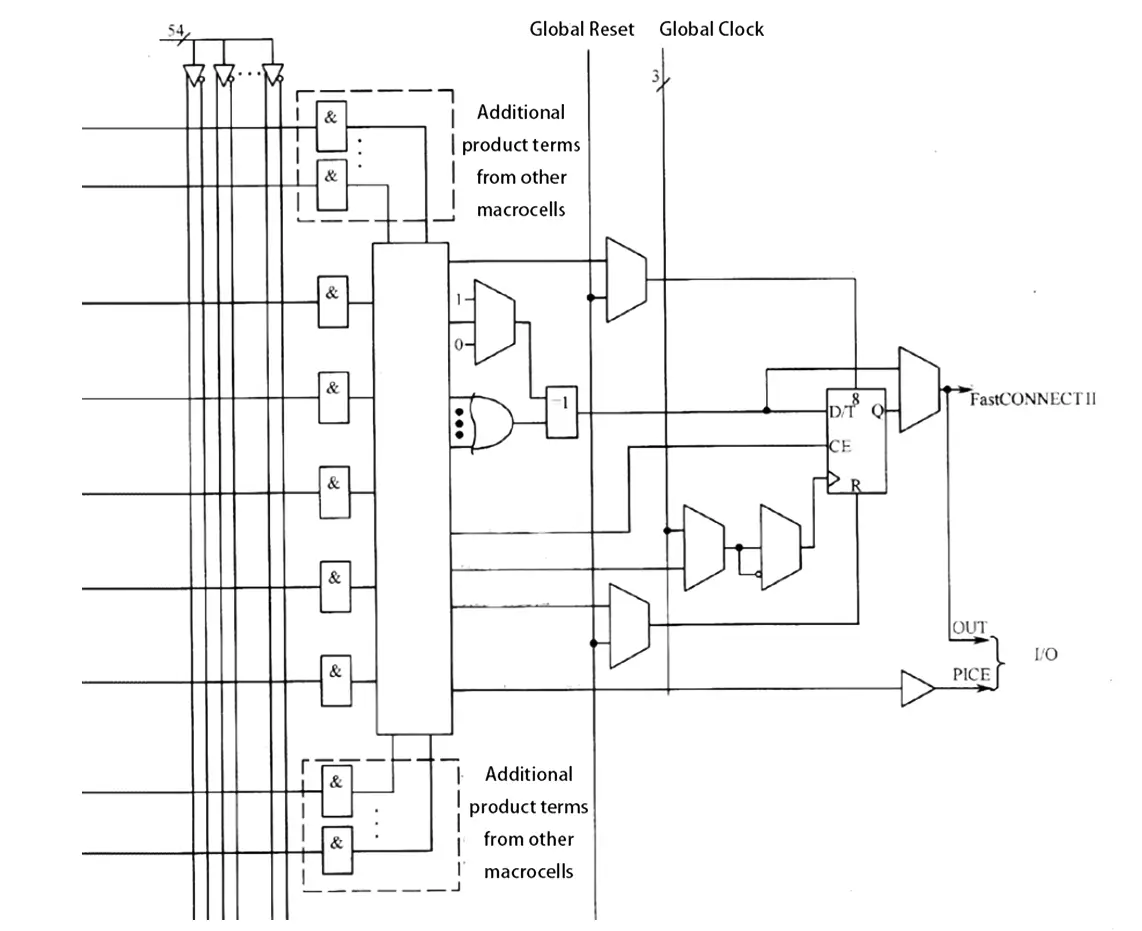

The macrocell, which is a crucial component of the CPLD, is responsible for executing fundamental logic operations. The basic structure of a macrocell is depicted in the image below. On the left side of the image, you can see a product term array, which may or may not be present, depending on the specific configuration.

Each cross-point within the product term array is programmable, and when activated, it performs “with” logic operations, contributing to the combination logic along with the product term allocator running in the background. This flexibility allows for the creation of various logic functions within the macrocell.

The programmable flip-flop on the right side of the image can be configured as either a D flip-flop or a T flip-flop, depending on the design requirements. If a trigger function is unnecessary, it can be bypassed, and the signal can be directed to the I/O pin or the connection matrix, providing versatility in designing and implementing different logic functions within the CPLD.

CPLD Components

CPLD components consist of various elements that collectively make up the architecture of the device. Here’s a detailed description of these components:

- Programmable Components: CPLDs utilize programmable components such as flash EPROM (Erasable Programmable Read-Only Memory), EEPROM (Electrically Erasable Programmable Read-Only Memory), PROM (Programmable Read-Only Memory), and ROM (Read-Only Memory). These components store configuration data and can be modified to define the device’s logic functions.

- Function Block: A function block within a CPLD comprises an AND plane, which receives inputs from I/O blocks, other function blocks, or even the outputs of the same function block. The inputs undergo logical operations and are then selected using a large multiplexer before being added to the OR array. This process allows for the creation of complex logic functions within the CPLD.

- Interconnect: The interconnect within a CPLD is a matrix of programmable switches that controls how signals are routed from one part of the device to another. It enables the establishment of connections between various elements, including function blocks and I/O blocks, to configure the desired logic.

- Input/Output Blocks: Input/Output (I/O) blocks are responsible for interfacing with external hardware. They ensure that signals are transferred to and from the CPLD pins at the appropriate voltage and current levels. I/O blocks contribute to reducing delays, minimizing the time the device needs to remain idle, and enhancing the overall resource utilization of the CPLD.

These components work together to provide flexibility and versatility in configuring complex digital logic functions within a CPLD while facilitating efficient communication with external devices.

Pros of CPLD

- It’s simple to design.

- It was developed at a modest cost.

- CPLD helps to make the board smaller.

- High reliability is provided by it.

Cons of CPLD

- A more advanced programmable logic device than an SPLD is a CPLD.

- It is a more intricate piece of programmable logic.

How does CPLD work?

CPLDs (Complex Programmable Logic Devices) employ various programming technologies, including CMOS EPROM, EEPROM, flash memory, and SRAM, to create highly compact, fast, and energy-efficient programmable logic devices. These devices fall within the category of large-scale integrated circuits, featuring relatively complex structures and substantial physical sizes. CPLDs are a type of digital integrated circuit that allows users to design and implement custom logic circuits tailored to their specific requirements.

The primary approach to designing with CPLDs involves the following steps:

- Develop the desired digital system using an integrated development software platform.

- Express the design using a hardware description language.

- Transfer the design code to the target CPLD chip through a download cable, a process known as “in-system” programming.

- Generate the corresponding target file that defines the logic functions to be realized by the CPLD.

FPGA Architecture

In the fundamental design of an FPGA (Field-Programmable Gate Array), three primary types of modules are employed. These modules are I/O blocks or pads, connector lines, switch matrices, and programmable logic blocks (CLBs). Users can interconnect these components in various configurations to create the basic architectural structure of an FPGA.

The functions of these FPGA architectural modules:

- CLB (Configurable Logic Block): The CLB is the core unit responsible for performing logic operations. It consists of logic elements and digital input and output connections. Users can configure the CLBs to implement custom logic functions as needed for their specific applications.

- Interconnects: The interconnects serve as pathways that convey instructions and data between the various logic blocks within the FPGA. These pathways enable the CLBs to collaborate in executing the user-defined logic.

- Switch Matrix: The switch matrix provides the necessary logic-based connections and routing between the components within the FPGA. It facilitates the dynamic configuration of connections, allowing for the flexibility to adapt the FPGA to different logic designs.

- I/O Pads: I/O pads serve as the interfaces between the FPGA and external devices or the outside world. They enable connections to be made with external hardware, allowing data to be transmitted to and from the FPGA.

The ability to link these modules in two-dimensional arrays and configure them according to specific requirements is a fundamental feature of FPGAs. This flexibility and programmability make FPGAs suitable for a wide range of applications, from digital signal processing to customizable hardware implementations.

FPGA Basics

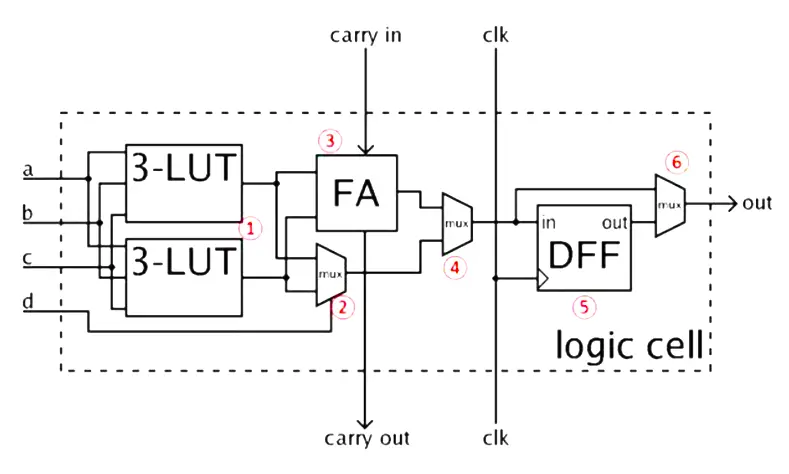

A single CLB (Configurable Logic Block) within an FPGA is composed of multiple logic blocks, each of which contributes to the CLB’s functionality. An important feature of an FPGA is its lookup table (LUT), which is distinctive to the technology. LUTs are capable of holding a predetermined list of logic outputs for every possible combination of inputs. Typically, LUTs come in versions with four to six input bits. Common logic operations that can be implemented using LUTs include flip-flops, full adders, and multiplexers.

The components within a CLB may vary in number and configuration depending on the specific FPGA device. In a simplified version, a CLB can consist of two three-input LUTs (1), a full adder (3), a D-type flip-flop (5), a regular multiplexer (2), and two programmable multiplexers within the FPGA.

A condensed CLB can operate in two different ways. In arithmetic mode, the full adder receives inputs from the LUT outputs and a carry input from another CLB. In normal mode, the LUTs and Multiplexer 2 work together to create a four-input LUT. Multiplexer 4 determines whether to use the full adder output or the LUT output. The decision of whether an operation is asynchronous or synchronized to the FPGA clock is determined by D flip-flop through Multiplexer 6.

In current-generation FPGAs, more advanced CLBs are capable of performing multiple operations within a single block. These advanced CLBs can be combined to execute more complex tasks such as multipliers, registers, counters, and even digital signal processing (DSP) activities, making FPGAs versatile for a wide range of applications.

FPGA Components

- The I/O Block is used to connect chips.

- Using programmable routing makes it possible to use functions.

- Logic functions can be implemented using programmable logic blocks.

Pros of FPGA

- FPGA development is less expensive than ASIC development because there are no NRE (Non-Recurring Expenses) and less expensive tools are used.

- FPGAs are always programmable at the software level. The FPGA IC may thus be reconfigured or reused indefinitely. FPGAs can also be remotely programmed.

- With HDL code, FPGA ICs may be easily programmed and are widely available. The consequence is a quicker release of the solution to the market.

- Routing, placement, and timing are handled by software in FPGA design. It necessitates less manual labor. Time-consuming and difficult place and router, floor planning, and timing considerations are eliminated by the design flow.

- FPGAs have the capability of logic-level programming. As a result, it might use more parallel and quicker signal processing. Execution by the CPU is difficult.

Cons of FPGA

- Basic knowledge of digital systems and the VHDL/Verilog programming languages are prerequisites for programming FPGAs. The programming is more complex than that used in equipment with processors. Additionally, engineers must understand how to use simulation software.

- The size and characteristics of the design are constrained by the resources available on the FPGA IC once it has been selected and used in the design. In order to prevent this issue, a suitable FPGA must be chosen from the beginning.

- The FPGA has increased power consumption, and programmers have little control over power optimization.

- FPGAs have gained popularity due to their versatility in various applications.

- Specific applications for FPGAs include voice recognition, cryptography, signal filtering, communication encoding, device controllers, software-defined radio, random logic, ASIC prototyping, medical imaging, computer hardware emulation, and device controllers.

- FPGAs are often used in specialized, low-volume applications where performance and cost dynamics make them a favorable choice.Prototyping and low-volume production work well with FPGAs. The cost per unit likewise grows as the number of FPGAs to be produced does.

- FPGAs (Field-Programmable Gate Arrays) are part of the family of programmable logic devices, often referred to as programmable hardware. They do not have inherent functionality on their own but can be programmed to behave as virtually any digital circuit one desires. This characteristic is remarkable because it allows for rapid configuration without the need for soldering or extensive wiring.

Here’s how FPGAs work:

- Configuration: FPGAs are configured by loading a specific bitstream configuration file onto the device. This configuration defines the interconnections and behavior of the logic elements within the FPGA.

- Versatility: Once configured, the FPGA will operate as the desired digital circuit. It can be easily reprogrammed to perform different tasks by loading a new configuration, making it highly versatile for a wide range of applications.

- RAM-Based: FPGAs use RAM-based configuration, which allows for dynamic reconfiguration. This means that the device can be updated and modified as needed without requiring physical changes.

- Description-Based Design: Designing for FPGAs typically involves describing the desired behavior rather than creating traditional circuit diagrams. Hardware description languages (HDLs) are commonly used to specify the functionality, and then tools are used to generate the corresponding hardware configuration.

CPLD Applications:

- Complex programmable logic circuits are well-suited for high-performance and demanding control applications.

- CPLDs can be used in digital designs to handle bootloader functions.

- They play a role in loading configuration data from non-volatile memory into field-programmable gate arrays.

- CPLDs are commonly used for straightforward design tasks such as address decoding.

- Their compact size and low power consumption make CPLDs suitable for price-sensitive, battery-operated portable devices.

FPGA Applications:

- FPGAs have gained popularity due to their versatility in various applications.

- Specific applications for FPGAs include voice recognition, cryptography, signal filtering, communication encoding, device controllers, software-defined radio, random logic, ASIC prototyping, medical imaging, computer hardware emulation, and device controllers.

- FPGAs are often used in specialized, low-volume applications where performance and cost dynamics make them a favorable choice.

FPGA vs. CPLD

| FPGA | CPLD |

| FPGAs, on the other hand, are short for field programmable gate arrays. | CPLDs stand for Complex Programmable Logic Devices. |

| On top of RAM is a digital logic chip called an FPGA. | Contrarily, CPLDs are EEPROM-based. |

| CPLD delays are far more predictable than FPGA delays. | Because CPLD has nonvolatile memory, it is more secure than FPGA. |

| The category of fine grain includes FPGA. | Contrarily, CPLD is of the coarse grain variety. |

| A Gate array and FPGA are comparable. | The CPLD, however, is the PAL’s counterpart. |

| Internal routing is dependable since it has little impact on FPGA performance. | On the other hand, the CPLD’s performance varies and is reliant on routing. |

| FPGA consumes more power. | In comparison, the CPLD has a reduced power usage. |

| FPGA is a good fit for complex apps. | However, the CPLD operates more well in simpler applications. |

| An FPGA has up to 100,000 small logic blocks. | CPLDs, in contrast, can only hold a small number of thousand logic blocks. |

| As opposed to this, an FPGA is a type of integrated circuit that is primarily made to be altered by a client or a developer after it is made. | A digital system’s operation is helped by a CPLD integrated circuit. |

The majority of vertical applications for FPGAs are specialized, low-volume ones. The best companies spend on the hardware expenses per unit for these low-volume applications. The number of practical applications has now risen as a result of the better performance dynamics and cost.

6G Controls - Leading Supplier of New & Original PLC 、DCS Parts and Automation Controller

6G Controls - Leading Supplier of New & Original PLC 、DCS Parts and Automation Controller